| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- 참고

- 전자공학

- Rectifier

- 반도체공정교육

- SoC설계

- pn junction

- 게임개발

- 다이오드

- 전자공학부

- 회로개발

- 베르의게임개발유튜브

- 자습포스팅

- 베르

- 하이포2기

- 자습목적포스팅

- 디지털회로설계

- UnrealEngine4

- diode

- 언리얼엔진4

- 자습

- 반도체교육

- 반도체소자교육

- 전자회로

- 반도체물성

- 개인스터디

- ASIC설계

- UE4

- 물리전자

- 반도체기초교육

- SK하이닉스

- Today

- Total

호경

[IDEC 교육] SoC 설계를 위한 AMBA On-Chip Interconnect 본문

※ 본 포스팅은 IDEC 교육을 듣고 스터디와 기록 목적을 위해 남긴 글입니다.

※ 강의 내용과 개인 스터디를 통해 적은 글이오니 틀린 내용이 존재할 수 있습니다!

[SoC 설계를 위한 AMBA On-Chip Interconnect]

1. What is SoC?

하나의 Chip안에 각종 IP(intellectual property : 지적 재산권), AP(Application Proccesor) 기타 User Interface들을 모두 넣은 것을 말한다.

2. Bus Interface

하나의 칩 내에서는 각 IP, AP, User interface들이 서로 상호 작용을 하며 동작을 해야된다. 각자가 모두 작동방식이 다르기 때문에 이를 총괄적으로 통신시켜줄 수 있는 것이 필요한데, 이 때 Bus를 사용한다.

이 때, 통신 규약으로 사용하는 것이 AMBA Protocol이고, 이는 SoC설계에 필수적인 Bus interface이기에 교육을 수강했다.

우선 AMBA Bus에 대한 내용을 정리하기 전에, Interconnect protocol에 어떤 동작들이 있는지 알아보자.

3. Interconnect Protocol

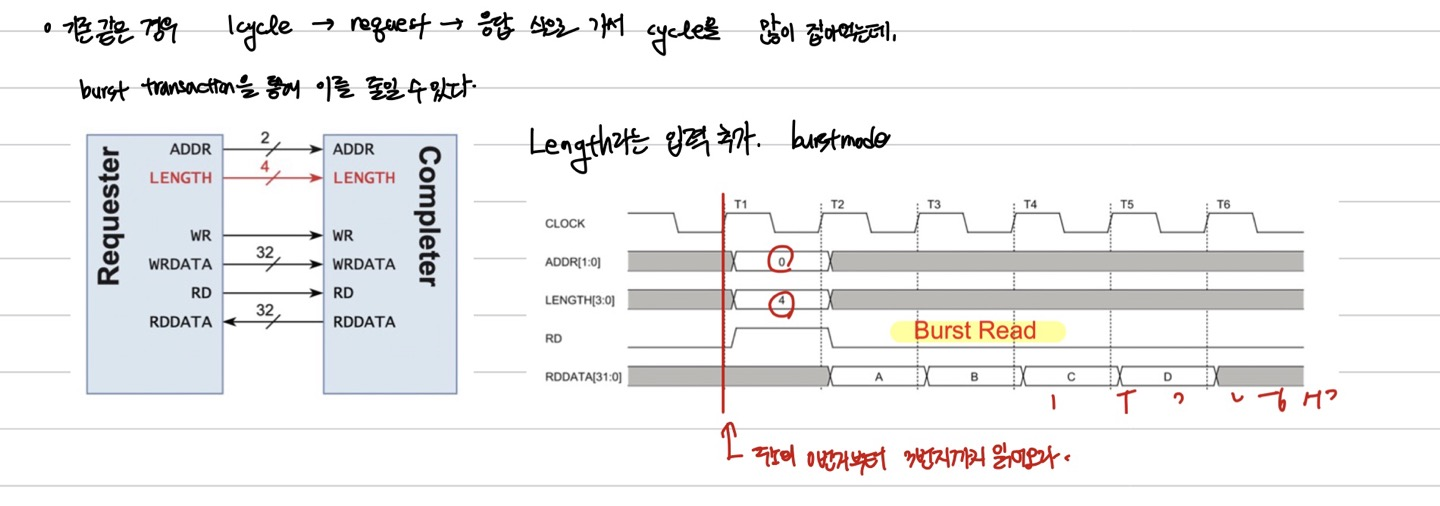

1) Burst Transactions

2) Back Pressure (Hand Shake 기법)

3) RDDATAVALID

★최종 Point-to-Point Summary

※ Interconnect 종류에는 On-chip과 Off-chip 방식이 있는데, SoC는 보통 On-Chip Interconnect를 사용한다.

4. AMBA

1) 소개

통신 규약에 해당한다.

2) 사용하는 이유

A. IP가 재사용 가능하다

B. Flexibility

C. Compatibility

3) AMBA 종류

A. AMBA AHB (이번 장에서 다룰 내용)

- Burst Transfers

- Split transactions

B. AMBA ASB

C. AMBA APB

5. AMBA-AHB

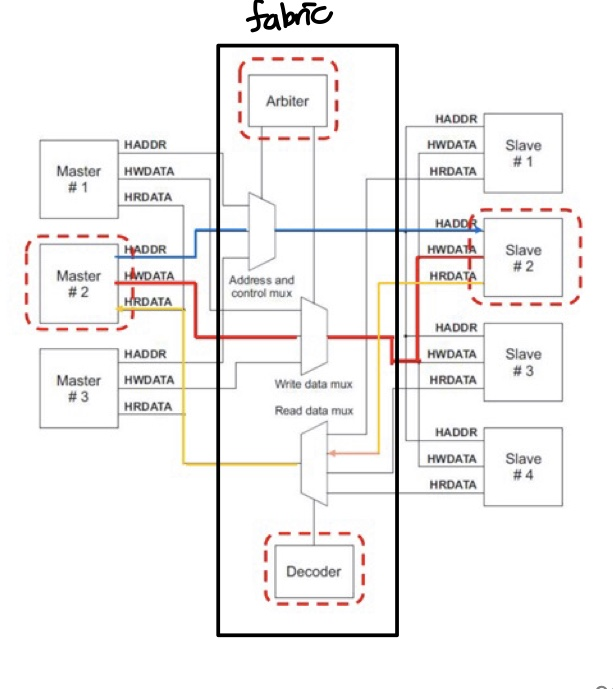

1) AMBA AHB 예시 Block Diagram

구조가 복잡해서 간단한 모식도로 나타내면 다음과 같다.

이는 AHB-LITE의 Extension으로 볼 수 있는데, AHB-LITE를 Multi-Layer 방식을 사용함으로써 multiple transaction이 가 능해진다.

아래와 같은 방식을 참고하면 될 듯하다.

6. AMBA-AHB-LITE

1) Block Diagram

AHB BUS는 Signal에 H를 붙여서 사용하고,

Manager와 Subordinate 모두 같은 HCLK에 동기되어 사용된다.

2) InterConnect까지 표현한 Block Diagram

HREADY와 HREADYOUT 신호는 Slave to Master에 해당하는 신호들이라고 보면된다.(Back pressure)

3) AHB-LITE Operations

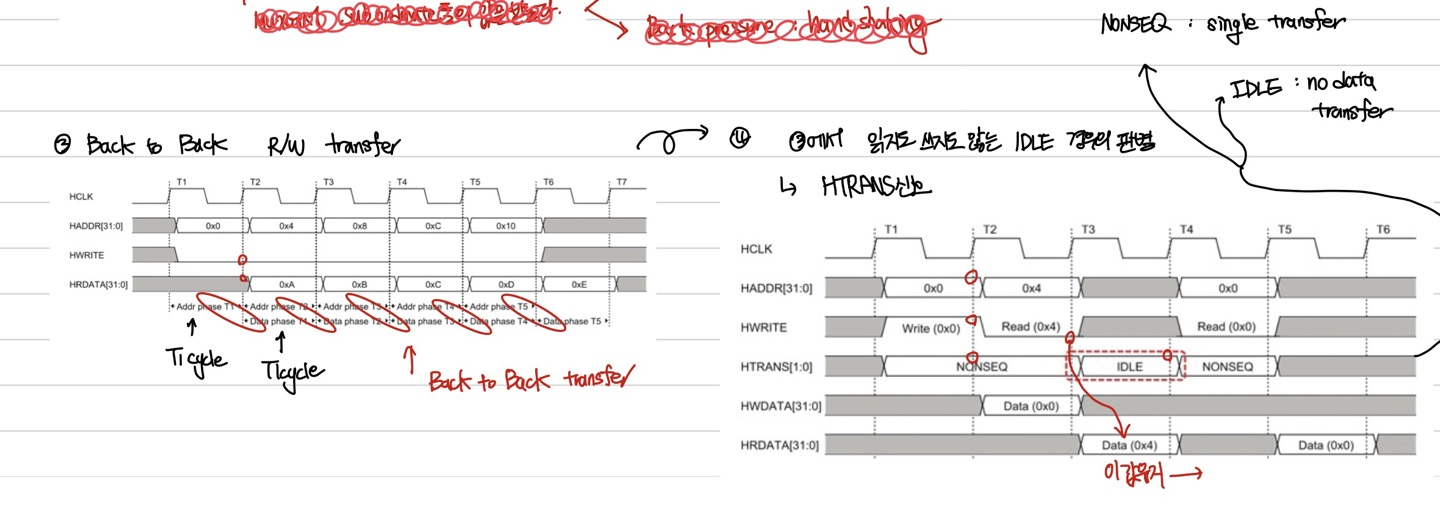

A. Back to Back R/W Transfer & HTRANS

Back to Back은 Address phase 1 cycle 뒤에 Data phase(R/W)가 오는데 이를 Back to Back operation이라고 한다.

그리고 HTRANS 신호는 Back to Back transfer에서 Read 혹은 Write가 일어나지 않는 상황인 IDLE에서는 Data 값을 유지하게 하는 신호이다.

B. HSIZE 신호

C. HBURST 신호

자세한 설명은 아래 필기에 적었다.

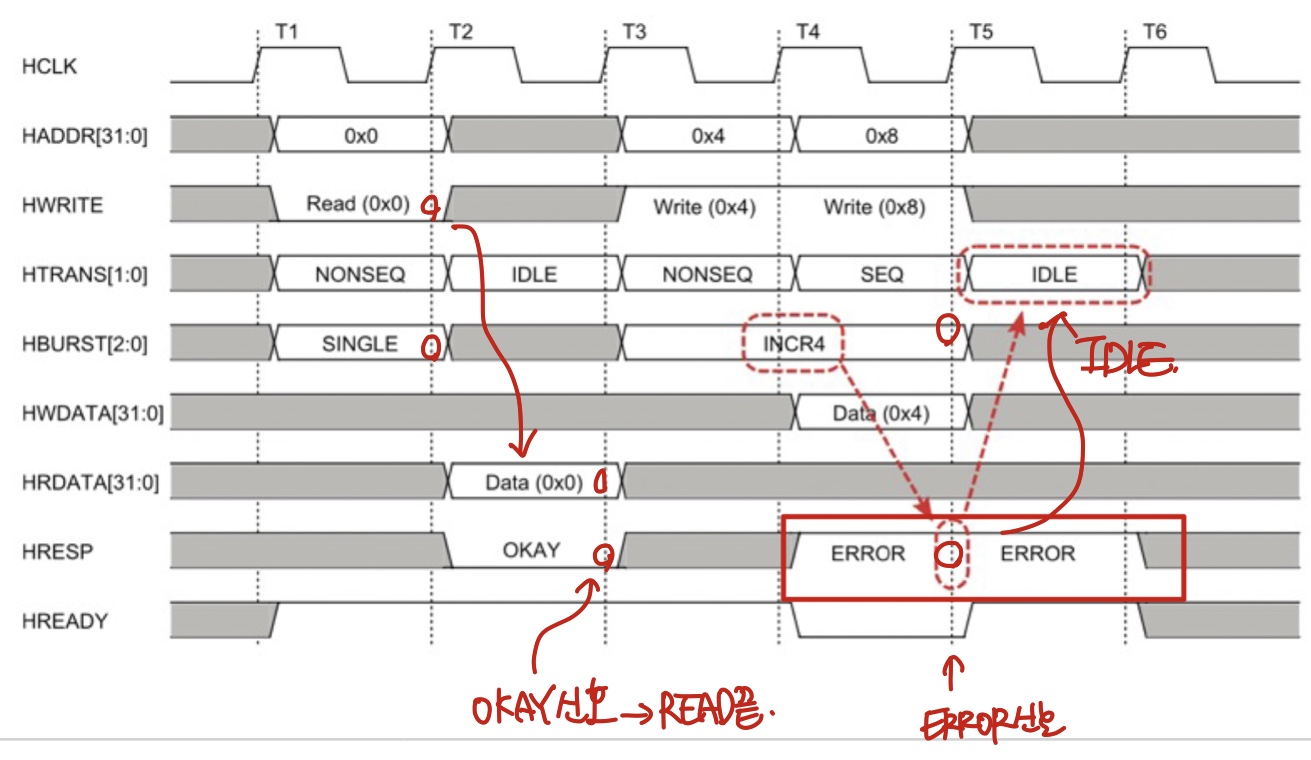

Timing Diagram을 통해서 WRAP4와 INCR4의 동작 과정을 살펴보자.

HSIZE를 통해 4byte가 들어가는 것을 확인할 수 있고, INCR4 신호를 받아 4byte의 data들이 Burst transfer가 되는 것을 볼 수 있다.

HSIZE를 통해 4byte의 Data 값들을 WRAP4 신홀르 받아 읽어오는 것을 볼 수 있다.

D. Back pressure

Back pressure를 통해 Master와 Slave간의 신호를 주고 받는다.

E. HRESP 신호

우선 여기서 끊어가고 다음 포스팅에 AXI BUS에 대해 간략하게 다루도록 하겠습니다.

'디지털회로설계 > SoC,ASIC 설계' 카테고리의 다른 글

| [개인스터디] DPRAM 설계 (0) | 2023.02.19 |

|---|---|

| [IDEC 교육] SoC 설계를 위한 AMBA On-Chip Interconnect (0) | 2023.02.19 |

| [개인스터디] Binary to BCD Code converter (0) | 2023.02.13 |

| [개인스터디/개인프로젝트] 8-bit 복합 ALU 설계하기 (0) | 2023.01.11 |

| [개인스터디] Loadable Counter and Test Bench (0) | 2023.01.08 |