| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- 전자회로

- 자습목적포스팅

- diode

- pn junction

- 반도체공정교육

- 베르의게임개발유튜브

- 반도체기초교육

- 물리전자

- UnrealEngine4

- 개인스터디

- 자습

- 전자공학

- 반도체소자교육

- 베르

- 회로개발

- 언리얼엔진4

- 반도체물성

- ASIC설계

- 자습포스팅

- 게임개발

- UE4

- 반도체교육

- SoC설계

- SK하이닉스

- Rectifier

- 참고

- 디지털회로설계

- 하이포2기

- 전자공학부

- 다이오드

- Today

- Total

호경

[IDEC 교육] SoC 설계를 위한 AMBA On-Chip Interconnect 본문

※ 본 포스팅은 IDEC 교육을 듣고 스터디와 기록 목적을 위해 남긴 글입니다.

※ 강의 내용과 개인 스터디를 통해 적은 글이오니 틀린 내용이 존재할 수 있습니다!

[SoC 설계를 위한 AMBA On-Chip Interconnect : AXI protocol]

1. AXI Protocol

Bus Specification으로 하는 것이 아니라, Manager와 Subordinate 별로 각자의 interface를 만들어서 point to point interface를 구성하는 통신 규약을 말한다.

AHB Bus에 비해서는 굉장히 복잡하지만 그만큼 기능들과 속도면에서 훨씬 장점들을 볼 수 있는 규약이다.

다음 모식도를 통해 간단하게 어떻게 AXI protocol을 이루는지 확인해보자.

그림과 같이 Manager와 Subordinate마다 각자의 interface를 가지고 있다. 이를 AXI protocol이라고 한다.

2. AXI Protocol 장점

1) Read와 Write 채널을 seperate 할 수 있다.

2) Multiple Outstanding Address, 이후에 설명할 예정이다.

3) Address와 Data phase 간의 타이밍 관계를 지킬 필요가 없다.(이후에 설명할 예정이고, AHB와 다른 점이다.)

4) Out-of Order Transaction을 지원한다.

3. AXI Channel

AXI 통신의 채널에는 대표적으로 다음과 같은 신호들이 존재한다.

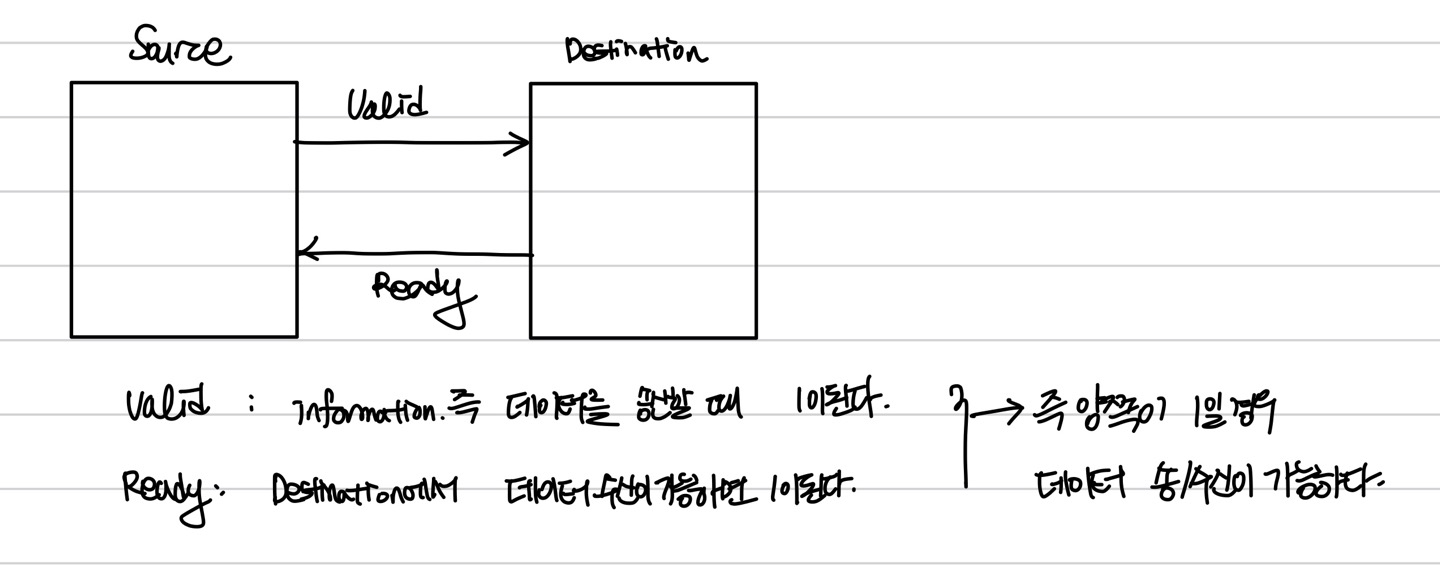

그리고 AHB와 마찬가지로 각 Channel별로 HandShake가 존재하는데, READY와 VALID로 다음과 같은 신호들이 있다.

4. AXI Data transfer & transactions

넘어가기 전에 용어 정의를 하고 가자.

Transfer와 Transaction이라는 용어가 있는데,

Transfer는 Source와 Destination 간의 "Single" 정보 교환에 해당하고,

Transaction은 앞서 언급한 Channel들의 "Multiple" 정보 교환에 해당한다.

간단히 말해 하나냐, 여러 개냐라고 보면 된다.

Transaction의 동작을 보기 전에 Transfer 동작을 보고 넘어가도록 하자.

1) Transfer Timing Example

Valid와 Ready의 Timing을 바꾸면서 Timing Diagram을 그렸다.

Ready랑 Valid가 모두 1이어야지 Data "Transfer"가 일어난다. 다음을 보면 이해가 될 것이다.

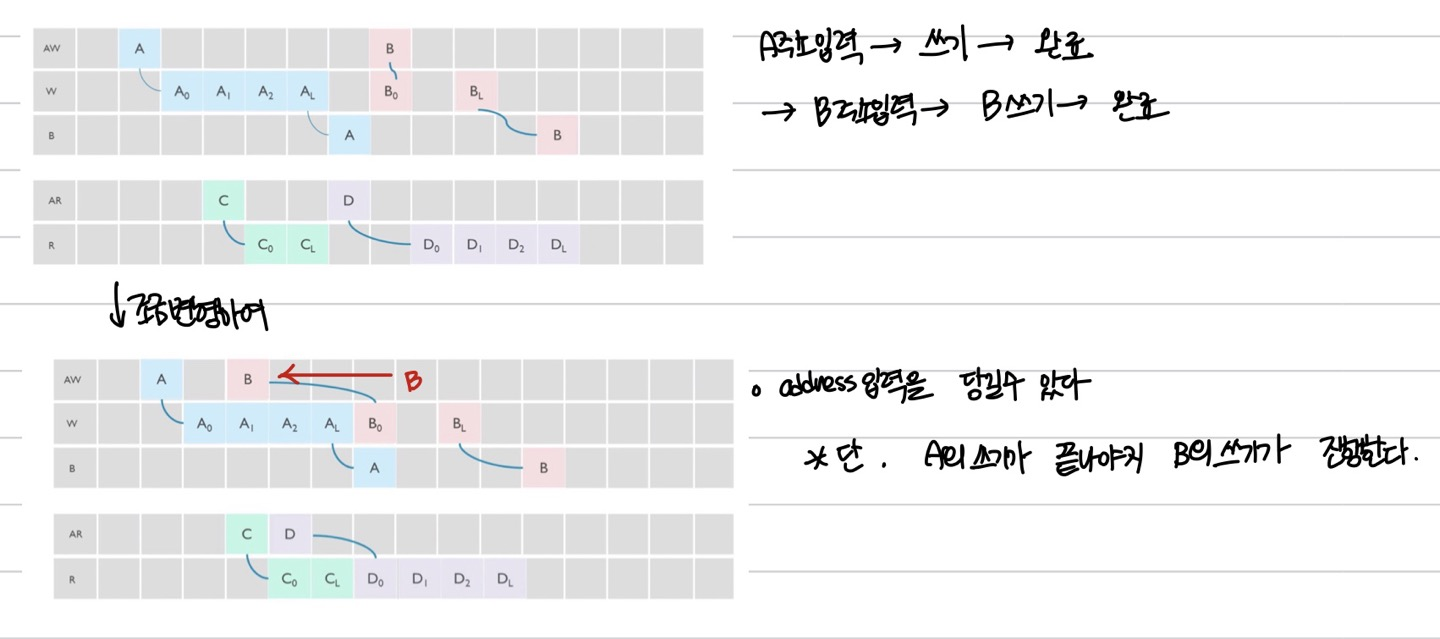

2) Transaction Timing Example

앞서 언급했듯이 "Multiple"의 정보 교환에 해당한다.

다음 timing diagram을 보자. (READ 동작은 WRITE와 매우 유사하여 생략했다.)

5. AXI : ID Tag

목차 2번 장점에서, AXI의 장점 중에 out of order와 multiple outstanding address와 data와 address phase 간의 타이밍 관계를 지켜도 되지 않은 장점들이 있다고 했다.

각 Channel에는 ID tag가 부여가 되는데 이 ID Tag는 Channel에서 Transaction 될 때 같이 발행이 된다.

ID Tag에 따라 Transaction의 순서가 완전히 달라질 수 있는데 이 얘기는 우선 뒤로 미뤄두자.

가장 먼저 Address phase와 Data phase간의 Back to Back timing relationship이 만족을 하지 않아도 되는데 다음을 보면 이해할 수 있다.

다음으로는 out of order 대해 알아보자.

앞서 언급했듯이 각 channel에서 Transfer가 발생될 때 ID Tag가 발행이 되는데, ID Tag에는 다음과 같은 특징이 존재한다.

a. 동일 ID Tag간에는 Order, 즉 순서가 지켜져야 한다.

b. 다른 ID Tag간에는 Order가 지켜지지 않아도 된다.

이를 통해 순서를 바꿀 수 있음으로써 out of order 기능이 수행된다.

6. Timing Diagram을 통한 AXI R/W 이해

다음 Timing Diagram을 보면 A와 C는 같은 ID Tag를 가지고 있기 때문에 A-C 순서로 처리가 돼야 하고 B는 다른 ID Tag를 가지고 있어 아무때나 처리가 되면 된다.

가능한 경우의 수는 다음과 같다.

A-B-C, A-C-B, B-A-C

1) Write ordering rules

2) Read ordering rules

다음 timing diagram에서 보면 Data Phase에서 각 order들은 정확히 지켜졌는데,

Read Data channel에서 B와 A가 번갈아가면서 처리된 걸 볼 수 있는데, 이는 Performance 향상을 위해서 발생한 Interleave이다. 이는 Write Data Channel에서 일어날 수 있다.

앞의 내용들은 정말 "개략적인" AXI와 AHB BUS 동작에 대한 내용들이었던 것 같다.

틀린 부분도 많은 것 같지만 최대한 머리를 짜내면서 이해해본 내용들이고, 틀린 지식이 있을 것 같아서 찾게 되면 그 때 그때마다 수정할 예정이다.

다음 포스팅에서는 AHB Burst와 AXI Burst를 비교하는 내용을 다룰 예정이고,

나도 아직은 제대로 이해하지 못한 Interleave에 대해서 공부해고 포스팅할 예정이다.

'디지털회로설계 > SoC,ASIC 설계' 카테고리의 다른 글

| [개인스터디] DPRAM 설계 (0) | 2023.02.19 |

|---|---|

| [IDEC 교육] SoC 설계를 위한 AMBA On-Chip Interconnect (0) | 2023.02.19 |

| [개인스터디] Binary to BCD Code converter (0) | 2023.02.13 |

| [개인스터디/개인프로젝트] 8-bit 복합 ALU 설계하기 (0) | 2023.01.11 |

| [개인스터디] Loadable Counter and Test Bench (0) | 2023.01.08 |