| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- 하이포2기

- SK하이닉스

- SoC설계

- pn junction

- UnrealEngine4

- 개인스터디

- 전자공학부

- Rectifier

- 디지털회로설계

- 반도체소자교육

- 회로개발

- 반도체공정교육

- ASIC설계

- 참고

- 반도체기초교육

- 자습목적포스팅

- 언리얼엔진4

- 베르의게임개발유튜브

- 반도체물성

- 반도체교육

- 물리전자

- 전자회로

- 다이오드

- 게임개발

- 전자공학

- 자습

- UE4

- 베르

- diode

- 자습포스팅

- Today

- Total

호경

5 - 3. Edge triggered D - Flip Flop 본문

※시작에 앞서, 학업을 위해 정리해 놓은 내용들이므로 틀린 부분이 있을 수 있습니다.

※더 나은 이해를 위해 차근차근 정리해 놓아 보았습니다.

안녕하세요. 오늘은 CLK 입력 신호를 포함하는 플립 플롭 중, D Flip Flop에 관하여 정리해보고자 합니다.

시작하기에 앞서, 글의 목차는 아래와 같습니다.

1. Edge triggered

1-1. Edge triggered의 의미

2. Edge triggered D - Flip Flop

2-1. Edge triggered D - Flip Flop의 내부구조와 AND - OR Circuit

2-2. Edge triggered D - Flip Flop의 진리표, 타이밍도

2-3. Edge triggered D - Flip Flop의 Orcad 구현

1. Edge triggered

1-1. Edge triggered의 의미

기억소자란 대분류에서 나아가, 래치와 플립플롭의 소분류에서 두 개의 차이점은 CLK 입력의 차이점임을 배웠습니다.

오늘 알아볼 D - Flip Flop은 총 두 가지 형태를 가지고 있습니다.

각각 상승에지트리거와 하강에지트리거에서 작동하는 D - Flip Flop입니다.

CLK 입력은 0과 1의 입력이 일정 주기를 가지며 입력되는 신호를 말합니다.

Symbol로 표현할 때는 단순히 negation symbol을 CLK 입력에 붙이면 됩니다.

symbol이 단순히 CLK 신호만은 가지지 않습니다. 다만, 이해를 위해 CLK 신호만을 타이밍도에서 표현해 보았습니다.

또한 작동되는 부분은 화살표 표시를 했습니다.

이 내용을 바탕으로 D - Flip Flop에 대해서 알아보겠습니다.

2. Edge triggered D - Flip Flop

2-1. Edge triggered D - Flip Flop의 내부구조와 AND - OR Circuit

D - Flip Flop은 두 개의 D - Latch의 연결로 이루어져 있습니다. Symbol로는 아래와 같이 나타낼 수 있습니다.

왼쪽 D - Latch에는 CLK 신호가 negation symbol에 의해 하강트리거에서 작동하도록 설계 되어 있으며,

오른쪽 D - Latch에는 CLK 신호가 그대로 입력되어 상승트리거에서 작동하도록 설계 되어 있습니다.

다음으로는 AND - OR Circuit으로 D - Flip Flop을 표현해 보겠습니다.

많이 복잡한 것 같습니다. 저도 여러 번 그리면서 회로를 그리게 되었습니다. 한 번 씩 꼭 그려 보시기 바랍니다.

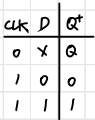

2-2. Edge triggered D - Flip Flop의 진리표, 타이밍도

D - Flip Flop의 진리표는 아래와 같습니다. 어떻게 보면 D - Latch와 매우 유사하다고 보아도 될 것 같습니다.

(단순히 G에 CLK 값을 입력 했으니깐요.)

CLK 신호가 0일 때는 이전 Q값이 그대로 출력이 되며, CLK 신호가 1일 때는 입력된 D 값이 들어감을 확인할 수 있습니다.

이를 바탕으로 임의로 값을 지정하여 타이밍도를 그려 보겠습니다.

동작에 대해 적어보았습니다.

ⓐ G1 = 1일 때, D = P 신호를 그대로 따라 갑니다.

ⓑ G1 = 0일 때, P는 다음 에지까지 이전 값을 유지합니다.

ⓒ G2 = 0일 때, Q는 다음 에지까지 이전 값을 유지합니다.

ⓓ G2 = 1일 때, P = Q 신호를 그대로 따라 갑니다.

해당 내용들을 조합해보면,

결론은 상승에지에서 D값이 그대로 Q가 됨을 확인할 수 있습니다. (이해가 되지 않으시면 직접 그려 보시는 방법도 좋습니다.)

2-3. Edge triggered D - Flip Flop의 Orcad 구현

마지막으로 Orcad로 D - Flip Flop을 구현해 보겠습니다.

Q와 Qn이 don't care로 출력되는 이유는

Pspice에서 설계한 회로는 초기값 Q를 지정해주지 않았기에 당연히 don't care로 출력이 됩니다.

마치기 전에, 중요한 내용을 마지막으로 얘기하고자 합니다.

회로도와 진리표를 통해 꼭 타이밍도를 그려 회로가 작동하는 과정을 다시 한 번 더 꼭 살펴보시기 바랍니다.

이상으로 Edge triggered D - Flip Flop에 대한 정리를 마치겠습니다.

'디지털회로설계 > 논리 회로 설계' 카테고리의 다른 글

| 1 - 2. 불 대수 : (추가) (0) | 2021.06.21 |

|---|---|

| 1 - 1. 불 대수 : 기본 동작 (0) | 2021.05.16 |

| 5 - 4. S.R - Flip Flop (0) | 2021.05.10 |

| 5 - 2. Gated G Latch, 게이트형 G 래치 (0) | 2021.05.09 |

| 5 - 1. 순차 논리 회로 소자 - S.R Latch (0) | 2021.05.09 |